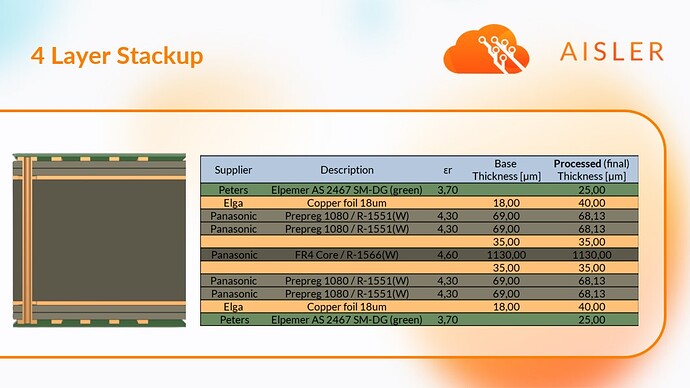

Stackup for 4-Layer Boards

We use Panasonic Prepreg 1080 Type R-1551(W) (58.9 KB), Peters coatings and Elga Copper foil.

Our Boards are RoHS and REACH compliant.

The following track layouts can be used to realise defined impedances. Please note that these values only provide a basic orientation. Interference factors such as angles, meanders or vias in the routing of the tracks may have a negative effect on the intended impedances.

| Type | Impedance | Signal- / Reference Layer | width | space | width |

|---|---|---|---|---|---|

| Single Ended | 50 Ω | TOP / IN1, BOT / IN2 | 245 µm | - | - |

| Differential pairs | 90 Ω | TOP / IN1, BOT / IN2 | 230 µm | 165 µm | 230 µm |

| Differential pairs | 100 Ω | TOP / IN1, BOT / IN2 | 190 µm | 180 µm | 190 µm |